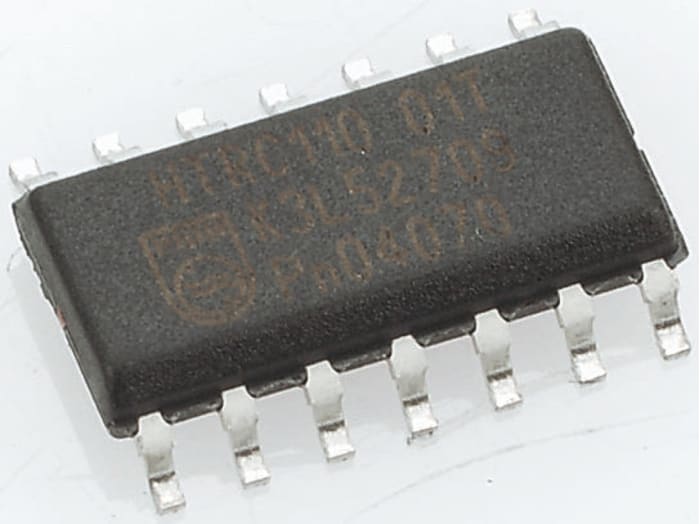

Techniniai dokumentai

Specifikacijos

Markė

NexperiaLogic Function

AND

Tvirtinimo tipas

Surface Mount

Number Of Elements

3

Number of Inputs per Gate

3

Schmitt Trigger Input

No

Pakuotės tipas

SOIC

Kaiščių skaičius

14

Logic Family

HC

Maximum Operating Supply Voltage

6 V

Maximum High Level Output Current

-5.2mA

Maximum Propagation Delay Time @ Maximum CL

100 ns @ 2 V, 17 ns @ 6 V, 20 ns @ 4.5 V

Minimum Operating Supply Voltage

2 V

Maximum Low Level Output Current

5.2mA

Aukštis

1.45mm

Plotis

4mm

Minimali darbinė temperatūra

-40 °C

Matmenys

8.75 x 4 x 1.45mm

Maksimali darbinė temperatūra

+125 °C

Propagation Delay Test Condition

50pF

Ilgis

8.75mm

Produkto aprašymas

74HC Family Logic Gates, Nexperia

A range of NXP standard Logic Gates from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.

74HC Family

€ 12,43

€ 0,218 Each (In a Tube of 57) (be PVM)

€ 15,04

€ 0,264 Each (In a Tube of 57) (su PVM)

57

€ 12,43

€ 0,218 Each (In a Tube of 57) (be PVM)

€ 15,04

€ 0,264 Each (In a Tube of 57) (su PVM)

Sandėlio informacija laikinai nepasiekiama.

57

Sandėlio informacija laikinai nepasiekiama.

Techniniai dokumentai

Specifikacijos

Markė

NexperiaLogic Function

AND

Tvirtinimo tipas

Surface Mount

Number Of Elements

3

Number of Inputs per Gate

3

Schmitt Trigger Input

No

Pakuotės tipas

SOIC

Kaiščių skaičius

14

Logic Family

HC

Maximum Operating Supply Voltage

6 V

Maximum High Level Output Current

-5.2mA

Maximum Propagation Delay Time @ Maximum CL

100 ns @ 2 V, 17 ns @ 6 V, 20 ns @ 4.5 V

Minimum Operating Supply Voltage

2 V

Maximum Low Level Output Current

5.2mA

Aukštis

1.45mm

Plotis

4mm

Minimali darbinė temperatūra

-40 °C

Matmenys

8.75 x 4 x 1.45mm

Maksimali darbinė temperatūra

+125 °C

Propagation Delay Test Condition

50pF

Ilgis

8.75mm

Produkto aprašymas

74HC Family Logic Gates, Nexperia

A range of NXP standard Logic Gates from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.